SystemVerilog Regions

Overview

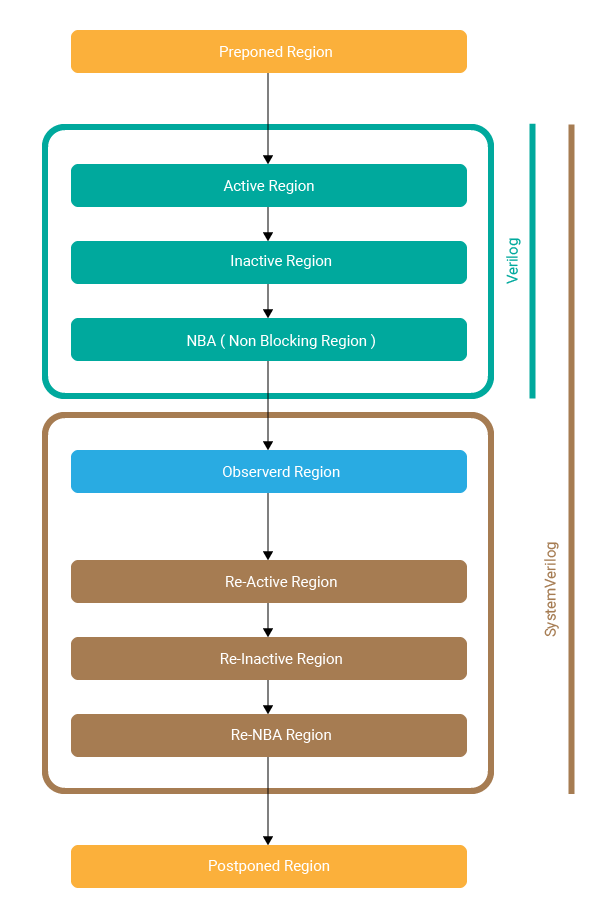

SystemVerilog's concept of "Scheduling Regions" is a crucial element influencing the execution flow of hardware designs. These regions determine the order of process and statement execution, impacting simulation behavior and final hardware implementation. Understanding scheduling regions empowers hardware engineers to optimize designs for performance, avoid pitfalls, and seamlessly integrate with various tools and verification methods. By grasping the fundamental aspects of SV Regions, designers can create efficient and robust HDL/HVL codes. Given below is a basic flow of the execution using the SV scheduling regions.

To better understand how regions work, you can review the verilog regions page using the following link.

Following is a diagram about the SystemVerilog regions for better pictorial understanding.

In SystemVerilog, along with Verilog regions, additional "Program Block" execution regions must also be considered. Any code which you wish to run in "Re-Regions" of SV, must be coded inside the program block. More can be found about this block in the next section.

Theory Questions

module top; initial begin $display( "A" ); end endmodule program pp; initial begin $display( "B" ); end endprogram

// A // B

module top; initial begin $display( "A" ); end endmodule program pp; initial begin #0; $display( "B" ); end endprogram

// A // B

Coding Questions

integer NUM = 10; // Global Variable Accessible TO Both Verilog Top Block and SystsemVerilog Program Block program top_p; initial begin $display( "%d | Post NBA Region Value", NUM ); NUM = 100; NUM <= 50; // Will update the RHS in NBA $display( "%d | Re-Active Region", NUM ); end initial begin #0; NUM = 70; $display( "%d | Re-Inactive Region (because of the #0)", NUM ); end initial begin #1; $display( "%d | After Re-NBA Region (printing this in the next time step)", NUM ); end endprogram module top; initial begin NUM <= 30; // Will update the RHS in NBA $display( "%d | Active Region", NUM ); end initial begin #0; NUM = 20; $display( "%d | Inactive Region (because of the #0)", NUM ); end endmodule