Assertions

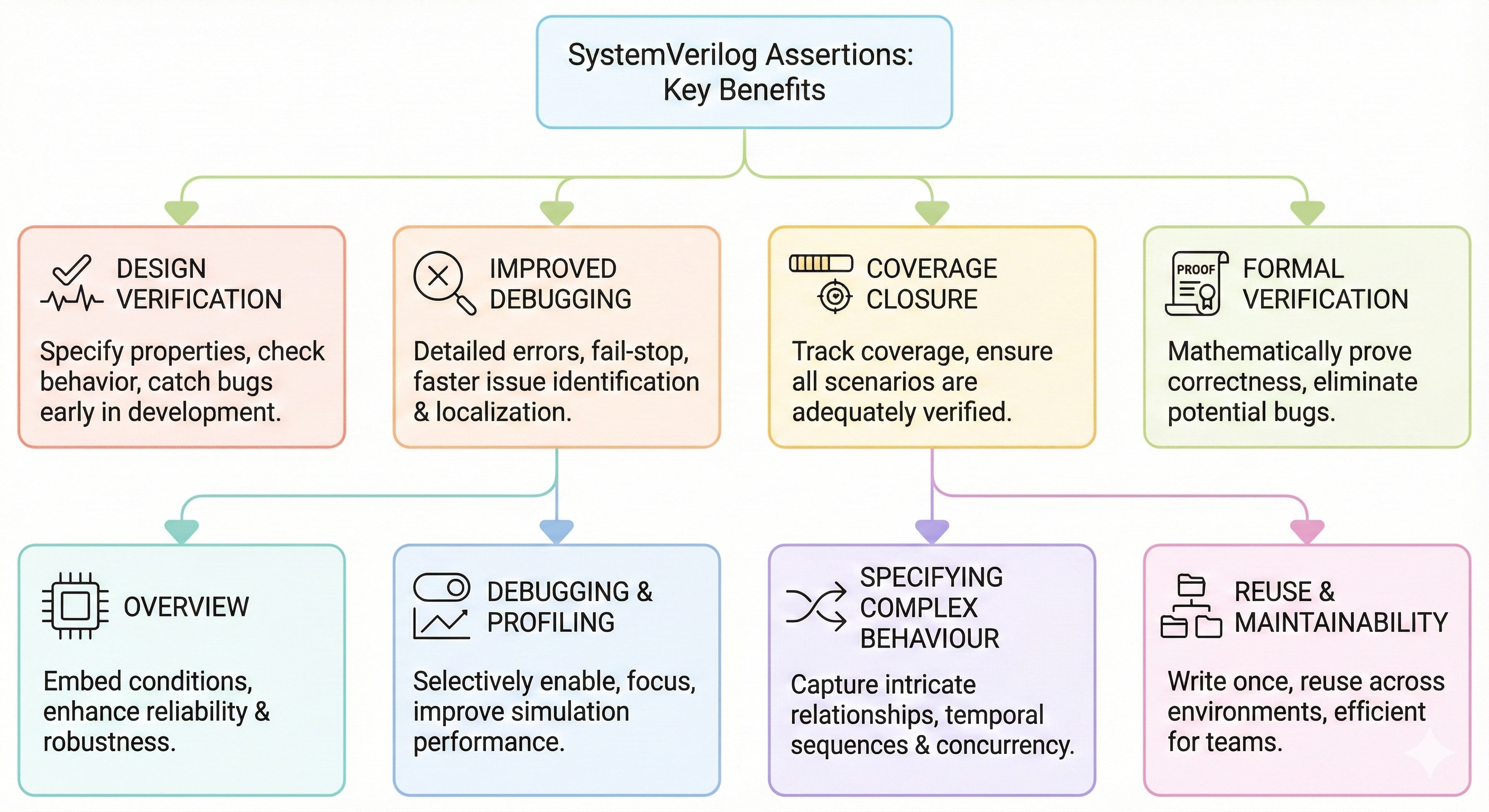

Overview

SystemVerilog assertions let engineers embed checks directly into hardware designs to ensure signals and behaviors follow expected rules. They can capture simple or complex conditions, automatically verify correctness during simulation, and help detect bugs early—improving the reliability and quality of digital systems.

Important Keywords

assert

assume

cover

assert #0

assert final

assume #0

assume final

cover #0

cover final

Keywords to be used in assertion sequences:

and

intersect

or

first_match

throughout

within

##

##[constant_range]

##[*]

##[+]

[=constant_range]

[->constant_range]

[*]

[+]

dist {}